- Sub-LVDS readout and decoding block

- SPI-based sensor configuration module

- Software library for sensor configuration

- Free running or triggered readout modes

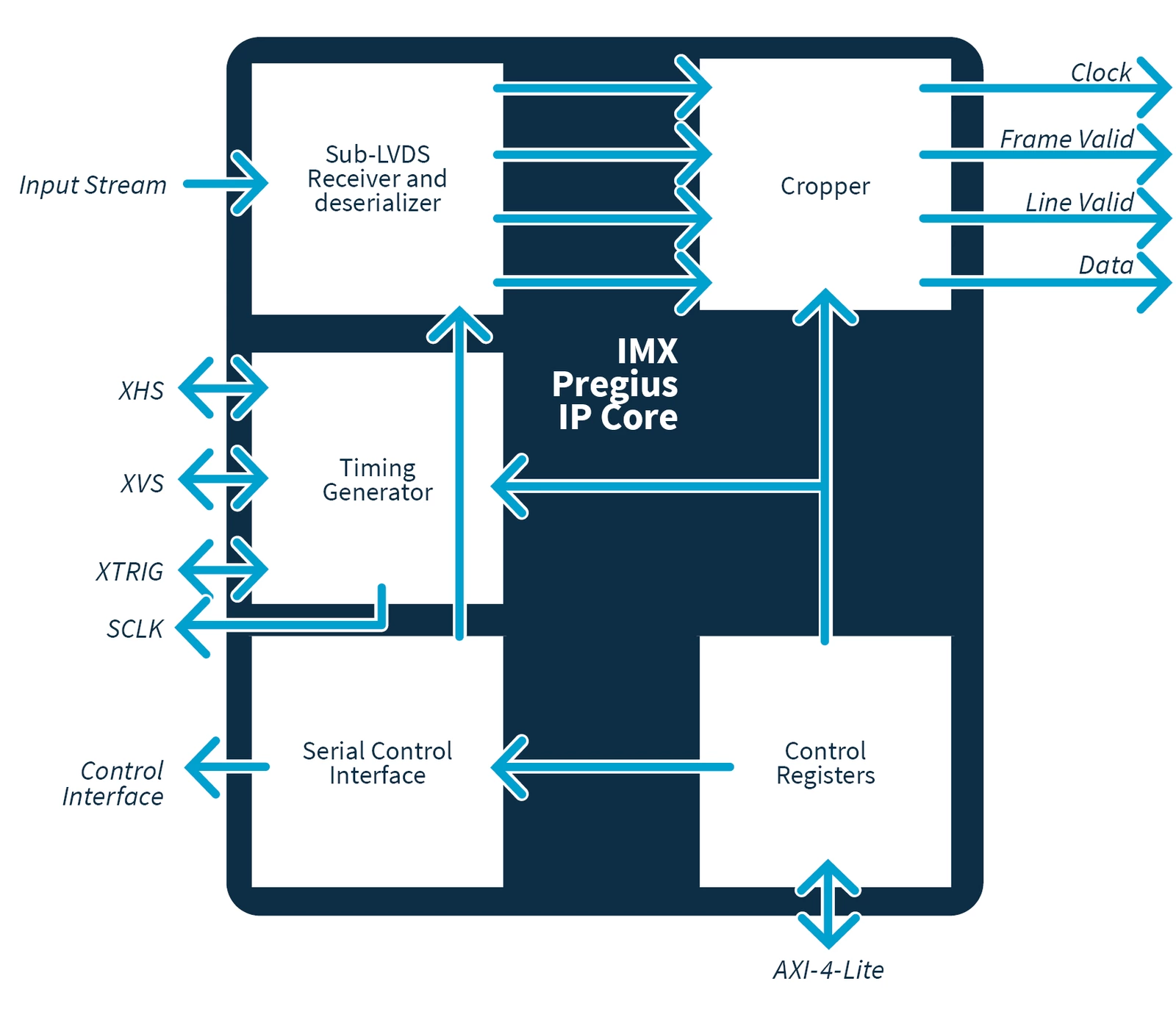

Architecture

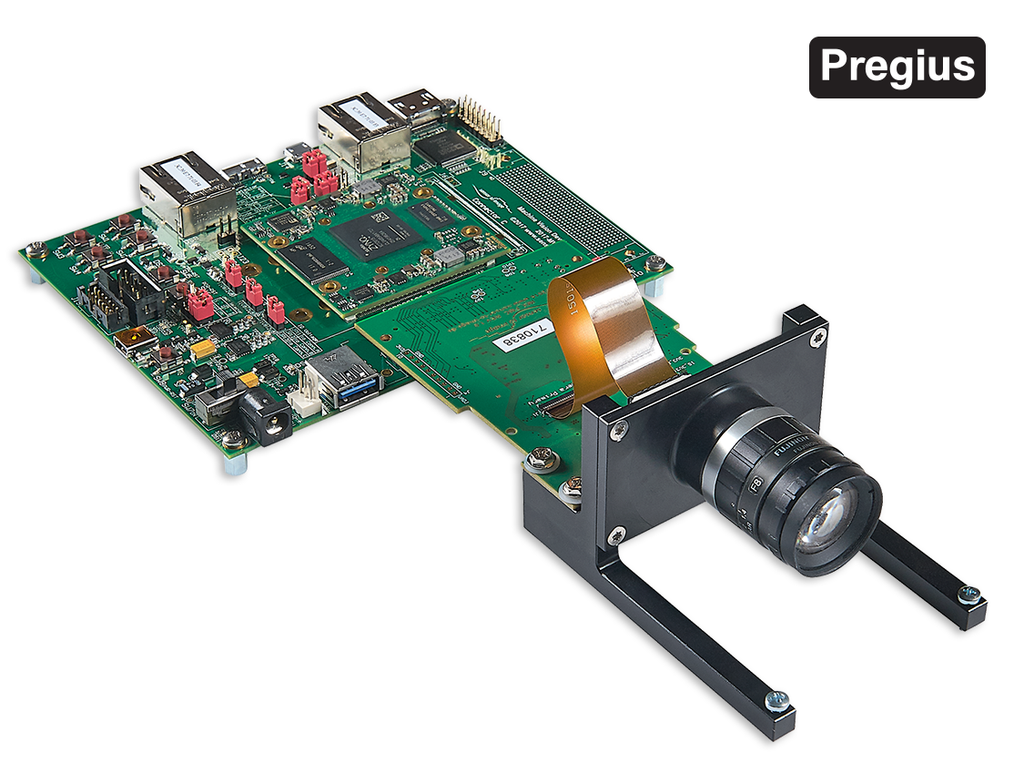

The IMX Pregius from Sony is a series of widely used, high quality CMOS image sensors. Allied Vision Schongau’s IMX Pregius IP Core supports these sensors, it is able to read their data as well as controlling them. It is delivered as a fully functioning reference design that is running on an agreed common delivery platform along with an FMC module compatible with Allied Vision Schongau’s MVDK and standard FPGA evaluation kits. Together, they provide an easy way to design a camera.

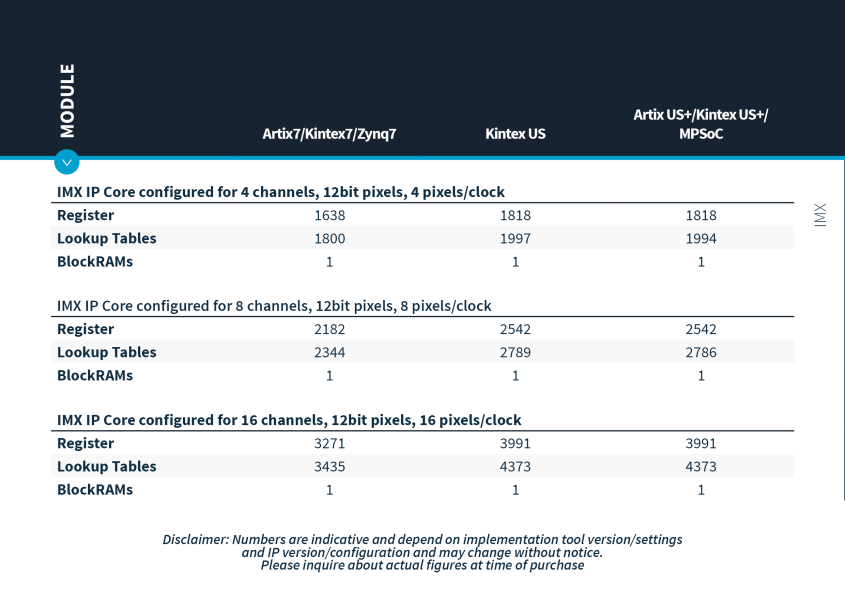

Resource Usage

Download resource usageBenefits

MVDK With IMX Pregius Interface Board

Trigger Generator

The IMX sensor itself can be used in free running mode or in slave mode using the IP Core’s timing and trigger generator. An SPI-based control interface enables sensor configuration, following the correct configuration timing.

Control Registers

The functionality of the IP core is configured either by parameters at compile time, or by Control Registers using an AXI-Lite interface at run time. A C software library configures the sensor and the IP core.

Supplied Reference Design

The IP core is delivered with a full reference design with GigE Vision interface, including an FMC (FPGA Mezzanine Card), which forms the interface between the sensor and a standard FPGA evaluation board. The FMC module is FMC-LPC compliant and does all power and level adaptations required by the IMX CMOS sensor. Depending on the licensing model, the IP Core may be delivered as encrypted VHDL or as VHDL source code. A software library to configure the sensor is included.

SubLVDS Receiver And Deserializer

The SubLVDS Receiver and Deserializer block is connected to the sensor’s output pins and uses the FPGA IO cells to deserialize the image stream. This block is highly FPGA dependent and currently limited to AMD FPGAs. The parallel video stream can be cropped and is presented in a Camera Link-like format for further processing.