GigE Vision Host IP Core

GigE Vision Host IP Core For FPGA

- Compact

- Customizable

- Compatible with AMD 7 Series (and newer) and Altera Cyclone 10 devices (and newer)

- Speed support from 1 Gbps to more than 10 Gbps

- Delivered as self-contained, fully-functioning reference design

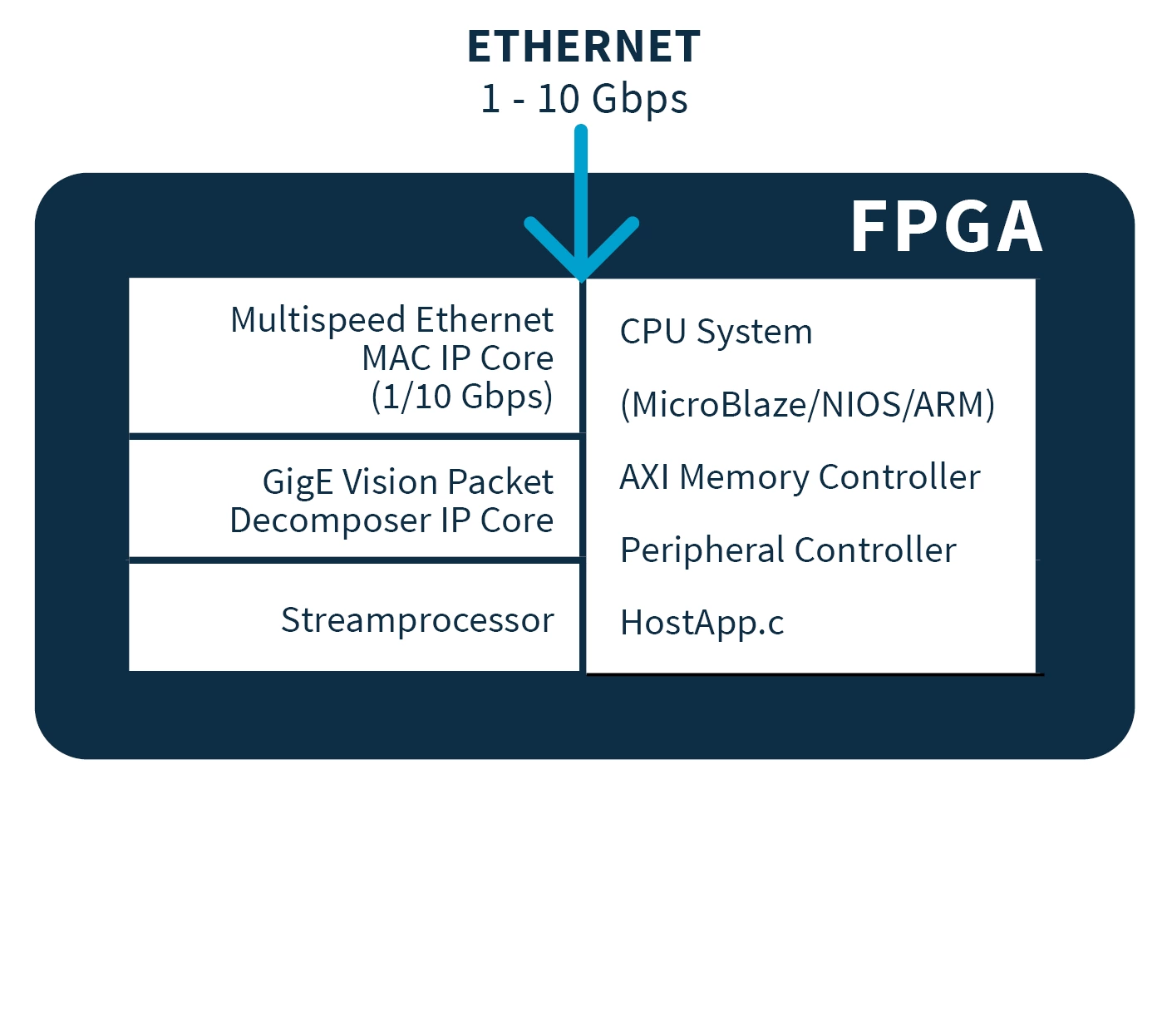

Architecture

GigE Vision is a standard communication protocol for vision applications based on the well-known Ethernet technology. It allows easy interfacing between GigE Vision devices and PCs running TCP/IP protocol family. Sensor to Image offers a set of IP cores and a development framework to build FPGA-based receiver products using the GigE Vision interface. Due to the speed of GigE Vision, especially at speeds higher than 1 Gbps, receivers require a fast FPGA based implementation of the embedded GigE core. The GigE Vision core set is compatible with AMD and Altera devices.

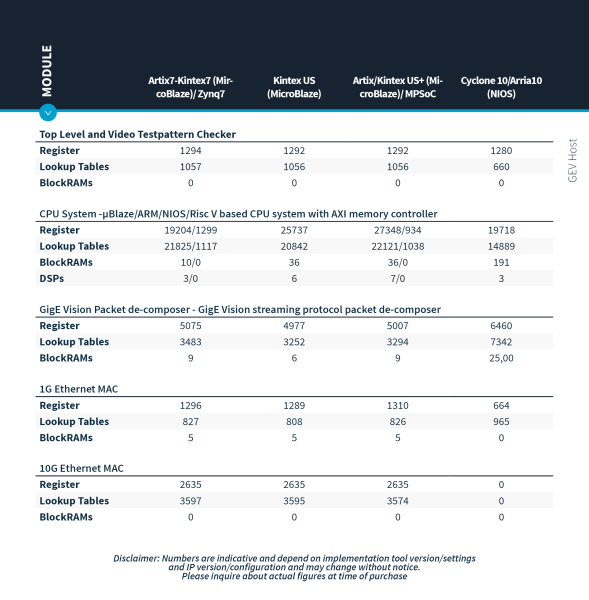

Resource Usage

Download resource usageBenefits

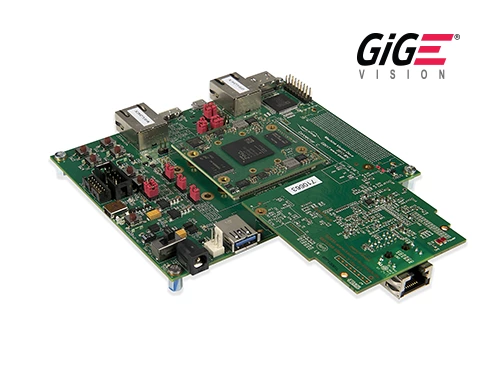

Broad Support Of FPGA Development Kits

Sensor to Image’s FPGA IP Cores are delivered as fully-working reference designs on an FPGA development kit. We support a wide range of off-the-shelf kits from AMD, Altera and Microchip.

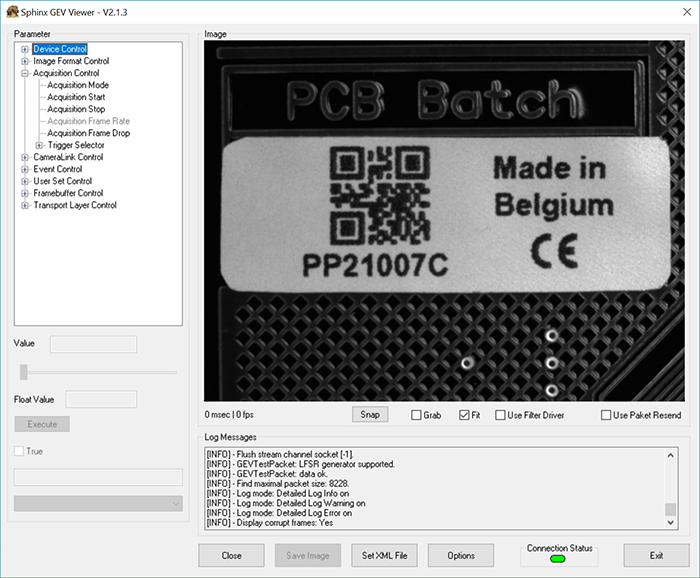

Sphinx SDK Included

A feature-rich software toolkit that provides the building blocks to quickly and easily design high-performance video applications that use minimal CPU resources. This also includes a filter driver and acquisition library for Windows or Linux along with sample applications, including GigE Vision/ GenICam compliant viewer.

Multistream Support

The GigE Vision Host IP has the capability to receive multiple data streams over one link. This is useful to acquire image data from several cameras. Note that it is highly recommended to run Linux on the embedded CPU for that use case.

Supplied Reference Design

Fully-functioning Reference Design: S2I’s FPGA solutions are delivered as a self-contained, fully-functioning reference design that is running on an agreed common platform along with FPGA IP Cores. This minimizes development time and allows for top-notch performance at a small footprint, while leaving enough flexibility to customize the design. Sensor to Image cores are compact and leave enough space in the FPGA for your application.

Top Level Design

The first component of the IP Core is the Top Level Design. It is an interface between external hardware (imager, sensors, GigE PHY) and FPGA internal data processing. We deliver this module as VHDL source code that can be adapted to custom hardware.

C Source Code For Software Library

The embedded GigE Vision library of the GigE Vision IP Core can optionally be delivered as source code. This is useful to extend functionality for rarely used optional GigE Vision features or to better tailor hardware requirements. An additional driver enables the use of Linux on the device.

GigE Packet De-Composer

The GigE Packet De-Composer extracts the video and control data from the packets stream. The GigE Packet De-Composer sends all GigE Vision control data to the CPU system and outputs the GigE Vision streaming data as an AXI-stream.

Sphinx GigE Vision Server

The delivery includes the Sphinx GigE Vision Server, which is a software Camera Simulator. The Sphinx GigE Vision Server helps to quickly get familiar with the design flow and shows how to communicate with third-party cameras.

Stream Processing Module

As an example of video processing, the reference design comes with a simple display unit or a pattern checker module, which demonstrates the usage of the video stream ouput of the GigE Packet De-Composer unit.

FPGA Integrated CPU

An FPGA integrated CPU design (MicroBlaze, NIOS, ARM, Risc V) is used for several non-time-critical network and configuration tasks. It also implements the GigE Vision Control Protocol (GVCP). This software is written in C and can be extended by the customer.

FMC Interface Extensions

To extend the functionality of the various reference boards, we provide FMC cards for 1G Ethernet and 10G Ethernet with NBaseT support.