- MIPI CSI-2 수신기 및 디코딩 블록

- 구성 가능한 MIPI 레인 수

- AMD D-PHY IP 사용

- 신속한 개발을 위한 작동 가능한 레퍼런스 디자인으로 제공

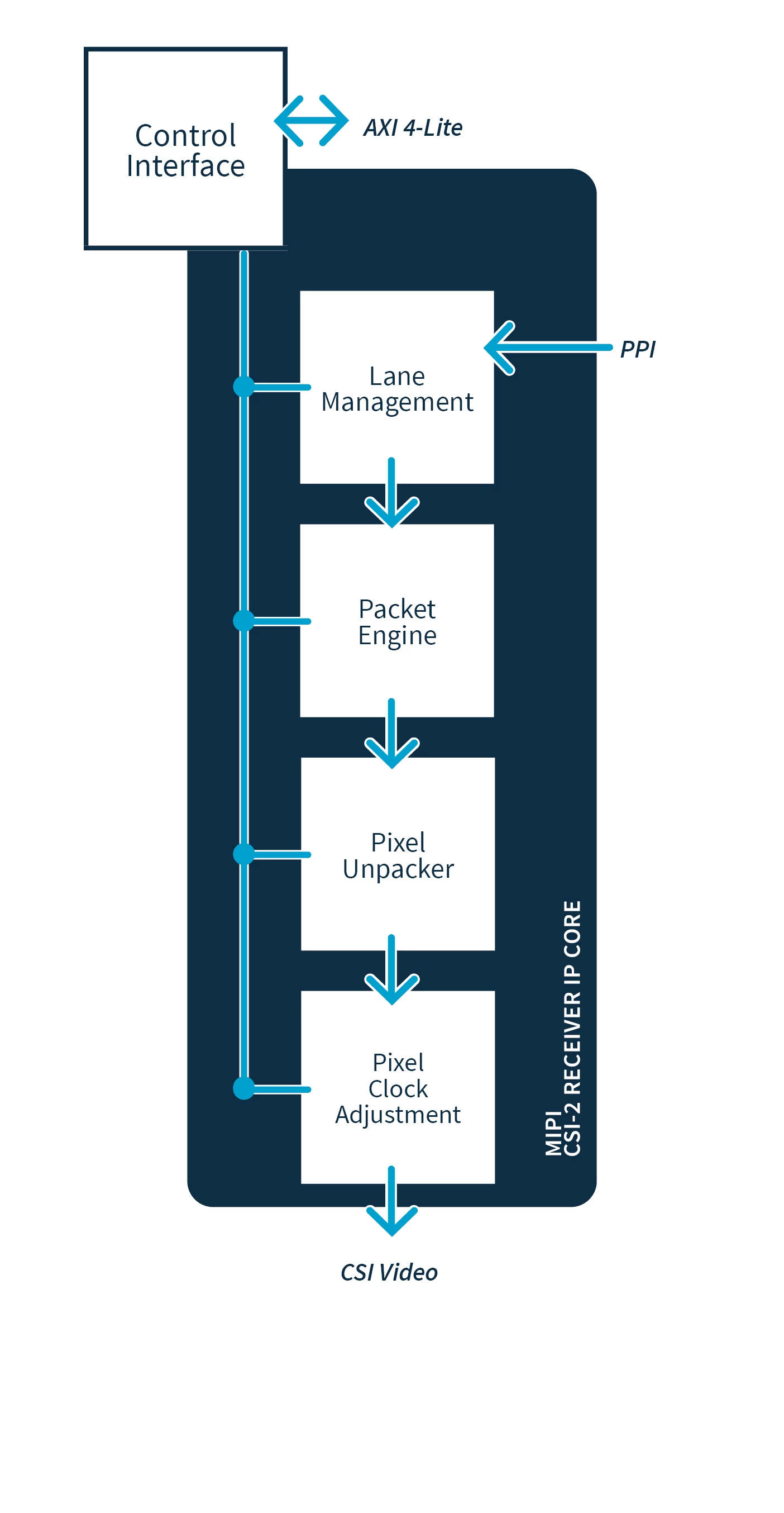

건축

MIPI 인터페이스를 갖춘 이미지 센서는 휴대폰뿐만 아니라 산업용 및 자동차 애플리케이션에도 사용됩니다. 이러한 애플리케이션은 제어 및 추가 처리를 위해 FPGA를 필요로 하는 경우가 많습니다. 본 IP는 다양한 벤더의 MIPI 센서를 FPGA에 연결하는 데 도움을 줍니다. 이 IP는 일반적으로 FPGA 벤더에서 제공하는 기존 D-PHY 구현을 기반으로 합니다. 본 IP는 S2I의 MVDK 및 표준 FPGA 평가 키트와 호환되는 MIPI FMC 모듈과 함께 합의된 공통 제공 플랫폼에서 실행되는 완전한 기능의 레퍼런스 디자인으로 제공됩니다. 이 조합은 카메라 설계의 간편한 방법을 제공합니다.

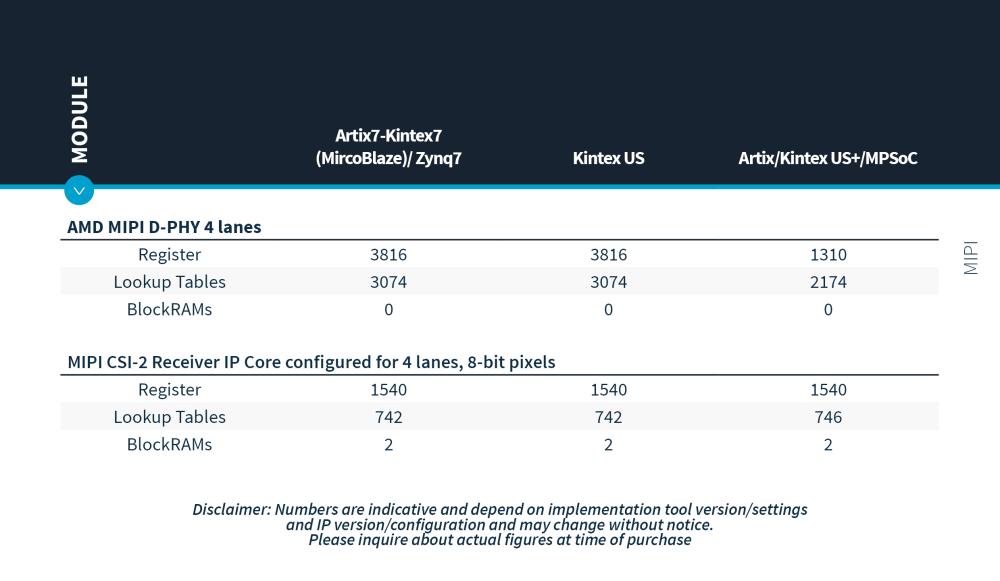

자원 사용량

리소스 사용량 다운로드혜택

MVDK MIPI CSI-2 인터페이스 보드

주요 기능

- FPGA 기술 독립적

- 다양한 D-PHY 구현체에 연결하기 위한 PPI 인터페이스

- 1, 2 또는 4개의 데이터 레인으로 구성 가능

- 모든 레인 속도 지원(사용된 FPGA에 의해 제한됨)

- RAW8, RAW10, RAW12, RAW14, RAW16 표준 MIPI 데이터 유형

- 임베디드 데이터 디코딩

- 픽셀 언패킹 없이 재정렬된 바이트 스트림 직접 출력

- AXI4-Lite 슬레이브 제어 인터페이스

배송

IP 코어는 Zynq7 또는 Ultrascale+ FPGA와 IMX MIPI FMC 모듈을 탑재한 S2I의 MVDK용 완전한 레퍼런스 설계와 함께 제공됩니다. 물리적 인터페이스가 AMD D-PHY 코어에 의해 추상화되므로, 예를 들어 7 시리즈 AMD FPGA와 같은 다른 FPGA 플랫폼으로 설계를 쉽게 이식할 수 있습니다.

사용 가능한 모듈

MIPI CSI-2 수신기 IP 코어는 암호화된 VHDL로 제공됩니다. 선택적으로 VHDL 소스 코드로도 제공됩니다. AMD Artix7, Kintex7, Zynq7 및 Ultrascale+ FPGA와 호환됩니다. MIPI CSI-2 수신기 IP 소프트웨어 라이브러리는 객체 파일로 제공됩니다. 선택적으로 C 소스 코드로도 제공됩니다.