- サブLVDS読み出し・復号ブロック

- SPIベースのセンサー設定モジュール

- センサー設定用ソフトウェアライブラリ

- フリーランニングまたはトリガ読み出しモード

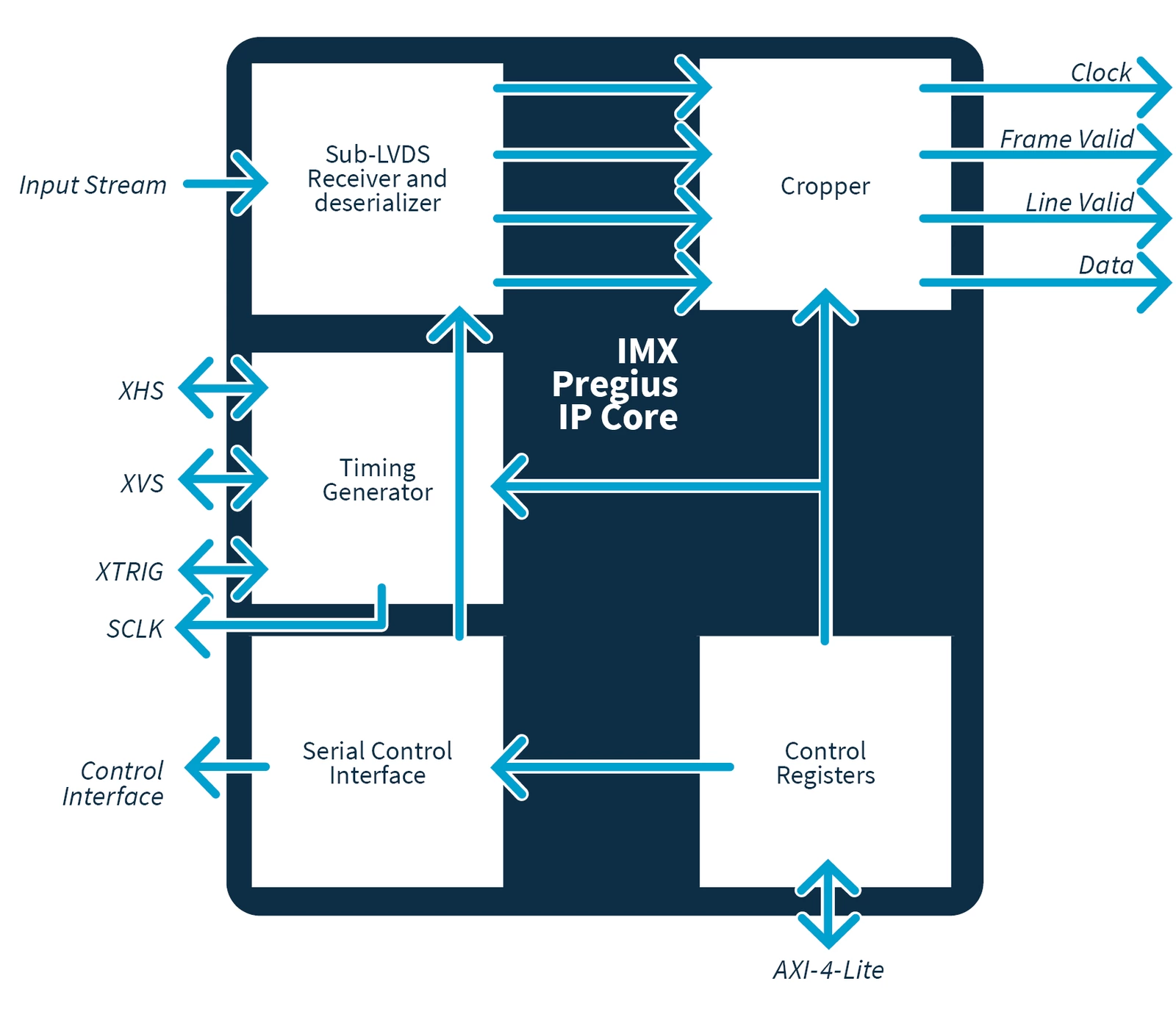

建築

ソニーのIMX Pregiusは、広く使用されている高品質CMOSイメージセンサーのシリーズです。 アライドビジョン・ショーンガウのIMX Pregius IPコアはこれらのセンサーをサポートし、データの読み取りと制御が可能です。これは、アライドビジョン・ショーンガウのMVDKおよび標準FPGA評価キットと互換性のあるFMCモジュールと共に、合意された共通提供プラットフォーム上で動作する完全機能の参照設計として提供されます。これらを組み合わせることで、カメラ設計を容易に行うことができます。

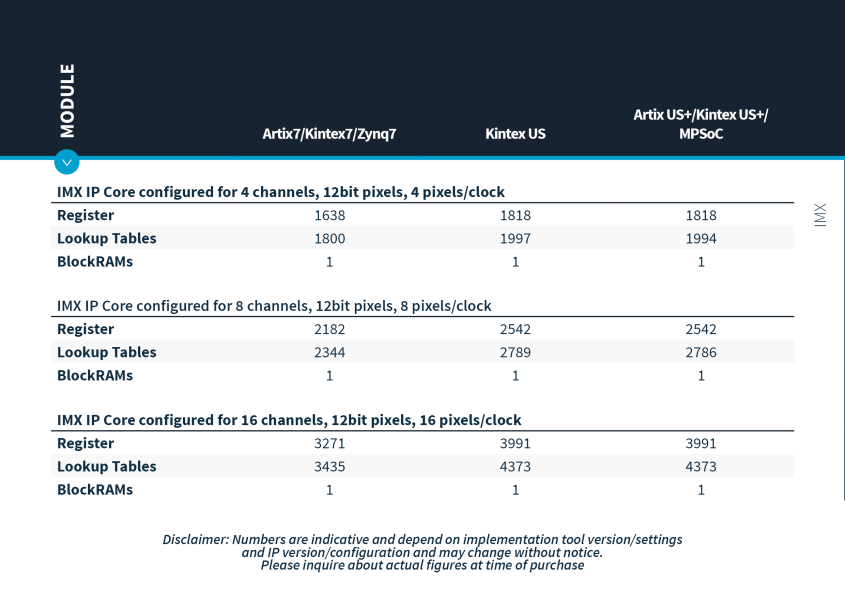

リソース使用量

リソース使用量のダウンロードメリット

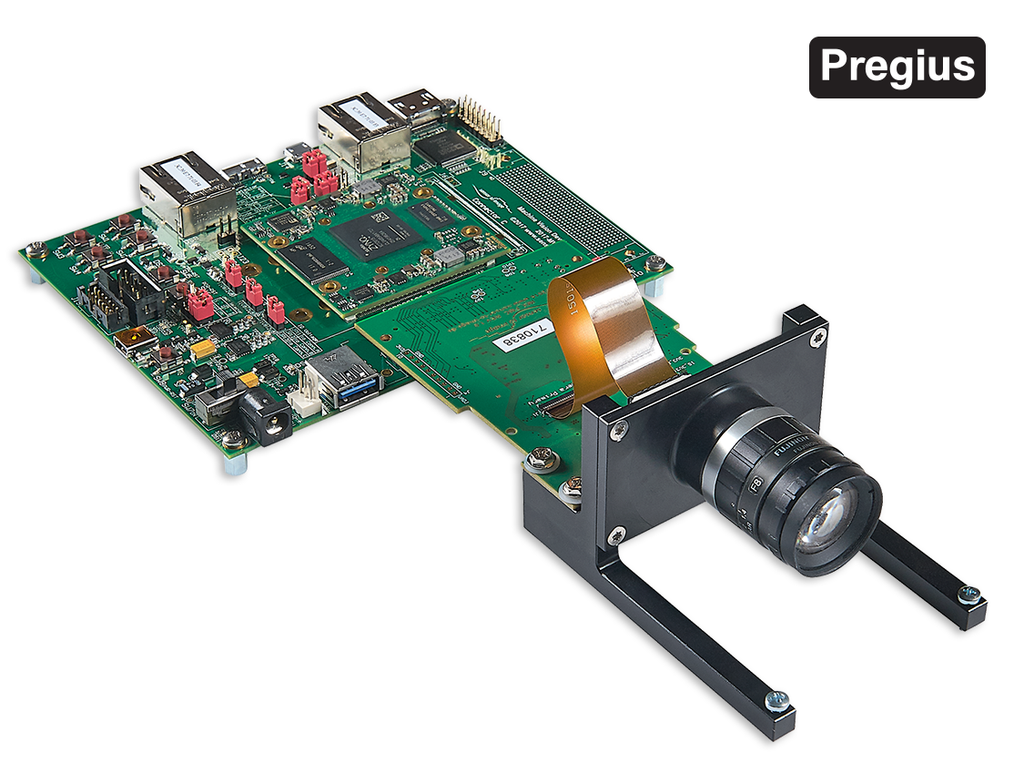

MVDK IMX Pregius インターフェースボード付き

トリガ発生器

IMXセンサー自体は、フリーランニングモードまたはIPコアのタイミングおよびトリガージェネレータを使用したスレーブモードで使用できます。SPIベースの制御インターフェースにより、正しい設定タイミングに従ってセンサー設定が可能です。

制御レジスタ

IPコアの機能は、コンパイル時のパラメータ設定、または実行時のAXI-Liteインターフェースを用いた制御レジスタによって設定される。C言語ソフトウェアライブラリがセンサーとIPコアの設定を行う。

提供されたリファレンス設計

IPコアは、GigE Visionインターフェースを備えた完全なリファレンスデザインと共に提供されます。これには、センサーと標準FPGA評価ボード間のインターフェースを形成するFMC(FPGAメザニンカード)が含まれます。 FMCモジュールはFMC-LPC準拠であり、IMX CMOSセンサーに必要な全ての電源およびレベル変換を実行します。ライセンスモデルに応じて、IPコアは暗号化されたVHDLまたはVHDLソースコードとして提供されます。センサー設定用のソフトウェアライブラリが含まれています。

サブLVDSレシーバおよびデシリアライザ

SubLVDSレシーバおよびデシリアライザブロックはセンサーの出力ピンに接続され、FPGAのI/Oセルを用いて画像ストリームをデシリアライズします。このブロックはFPGAへの依存度が高く、現在はAMD製FPGAに限定されています。並列ビデオストリームはクロップ可能であり、さらなる処理のためにCamera Link類似のフォーマットで出力されます。