GigE Vision ホスト IPコア

GigEビジョン ホスト IPコア for FPGA

- コンパクトな設計

- カスタマイズ可能

- AMD 7シリーズ(およびそれ以降)およびAltera Cyclone 10デバイス(およびそれ以降)に対応

- 1 Gbpsから10 Gbps以上の速度をサポート

- 独立した完全機能のリファレンスデザインとして提供

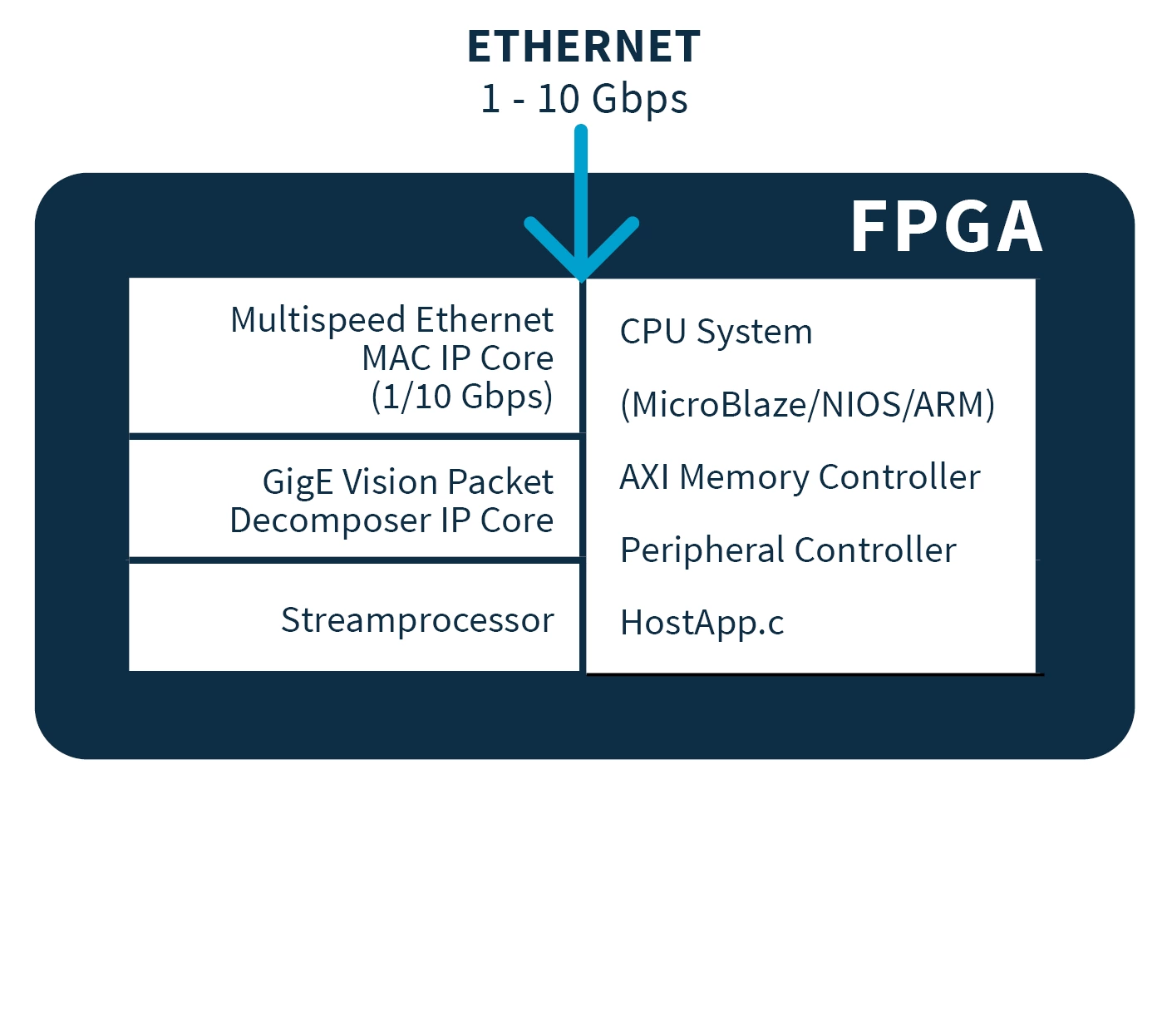

建築

GigE Visionは、広く普及しているイーサネット技術に基づく、ビジョンアプリケーション向けの標準通信プロトコルです。これにより、GigE VisionデバイスとTCP/IPプロトコルファミリを実行するPC間の容易なインターフェースが可能となります。 Sensor to Imageは、GigE Visionインターフェースを用いたFPGAベースの受信機製品を構築するための一連のIPコアと開発フレームワークを提供します。GigE Visionの速度、特に1Gbpsを超える速度では、受信機には組み込みGigEコアの高速FPGA実装が求められます。GigE VisionコアセットはAMDおよびAlteraデバイスと互換性があります。

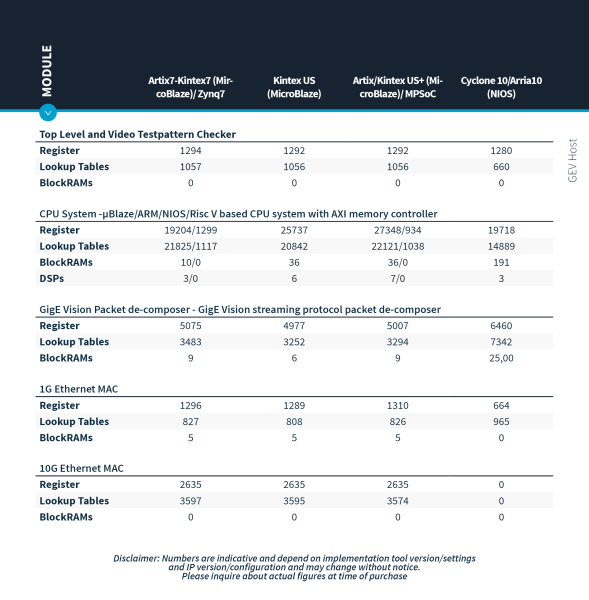

リソース使用量

リソース使用量のダウンロードメリット

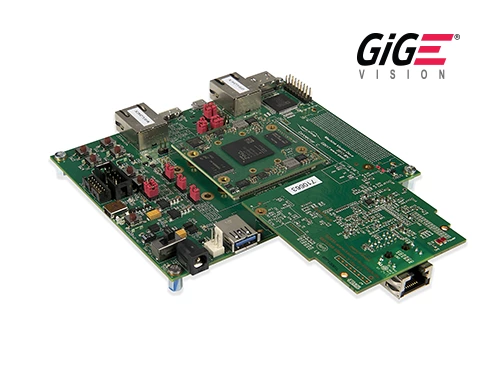

FPGA開発キットの幅広いサポート

Sensor to ImageのFPGA IPコアは、FPGA開発キット上で完全に動作するリファレンスデザインとして提供されます。AMD、Altera、Microchipなど、幅広い市販キットをサポートしています。

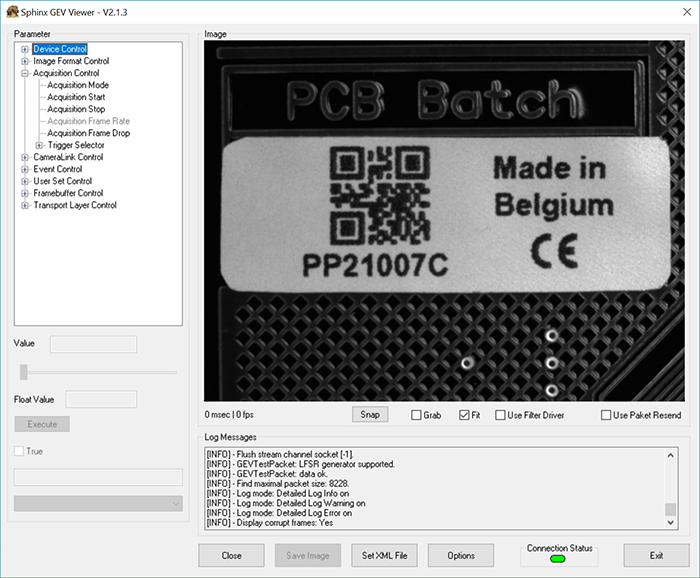

Sphinx SDK 付属

豊富な機能を備えたソフトウェアツールキットで、最小限のCPUリソースで動作する高性能ビデオアプリケーションを迅速かつ容易に設計するための基盤を提供します。これにはWindowsまたはLinux向けのフィルタードライバーと取得ライブラリ、およびGigE Vision/GenICam準拠ビューアを含むサンプルアプリケーションが含まれます。

マルチストリームサポート

GigE VisionホストIPは、1つのリンク上で複数のデータストリームを受信する機能を備えています。これは複数のカメラから画像データを取得する際に有用です。なお、このユースケースでは組み込みCPU上でLinuxを実行することが強く推奨されます。

提供されたリファレンス設計

完全機能リファレンス設計:S2IのFPGAソリューションは、合意された共通プラットフォーム上で動作するFPGA IPコアと共に、自己完結型の完全機能リファレンス設計として提供されます。これにより開発時間を最小限に抑え、小さなフットプリントで最高水準の性能を実現すると同時に、設計のカスタマイズに十分な柔軟性を確保します。Sensor to Imageコアはコンパクトなため、FPGA内にアプリケーション用の十分なスペースを確保できます。

トップレベルデザイン

IPコアの最初の構成要素はトップレベル設計です。これは外部ハードウェア(イメージャ、センサー、GigE PHY)とFPGA内部のデータ処理間のインターフェースです。このモジュールはカスタムハードウェアに適合可能なVHDLソースコードとして提供します。

ソフトウェアライブラリ用C言語ソースコード

GigE Vision IPコアに組み込まれたGigE Visionライブラリは、オプションでソースコードとして提供可能です。これは、使用頻度の低いGigE Visionのオプション機能を拡張したり、ハードウェア要件をより適切に調整したりするのに有用です。追加のドライバにより、デバイス上でLinuxを使用することが可能になります。

GigE パケット分解器

GigEパケット分解器は、パケットストリームからビデオデータと制御データを抽出します。GigEパケット分解器は、すべてのGigE Vision制御データをCPUシステムに送信し、GigE VisionストリーミングデータをAXIストリームとして出力します。

スフィンクス GigE Vision サーバー

納品物には、ソフトウェアカメラシミュレータであるSphinx GigE Vision Serverが含まれます。Sphinx GigE Vision Serverは設計フローの習得を迅速に支援し、サードパーティ製カメラとの通信方法を示します。

ストリーム処理モジュール

ビデオ処理の一例として、リファレンス設計には簡易表示ユニットまたはパターンチェッカーモジュールが付属しており、GigEパケット分解ユニットのビデオストリーム出力の使用方法を実証します。

FPGA統合CPU

FPGAに統合されたCPU設計(MicroBlaze、NIOS、ARM、Risc V)は、複数の非時間依存ネットワークおよび設定タスクに使用されます。また、GigE Vision制御プロトコル(GVCP)も実装しています。このソフトウェアはC言語で記述されており、顧客による拡張が可能です。

FMCインターフェース拡張機能

各種リファレンスボードの機能拡張のため、1Gイーサネットおよび10Gイーサネット対応のFMCカード(NBaseTサポート付き)を提供します。