- MIPI CSI-2-Empfänger und Decodierungsblock

- Konfigurierbare Anzahl von MIPI-Lanes

- Verwendung von AMD D-PHY IP

- Lieferung als funktionsfähiges Referenzdesign für eine schnelle Entwicklung

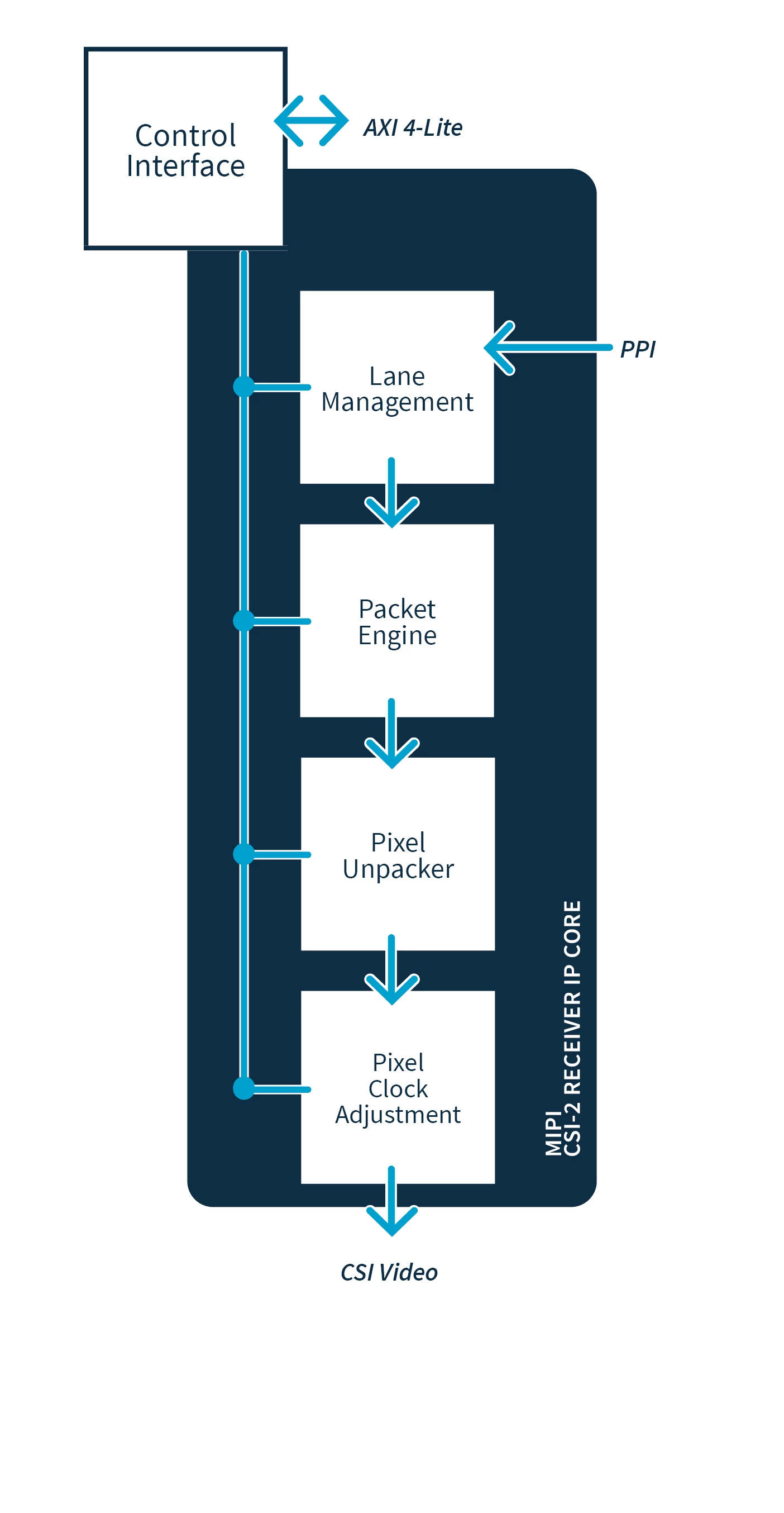

Architektur

Bildsensoren mit MIPI-Schnittstelle werden nicht nur in Mobiltelefonen, sondern auch in Industrie- und Automobilanwendungen eingesetzt. Diese Anwendungen erfordern häufig einen FPGA für die Steuerung und Weiterverarbeitung. Diese IP hilft bei der Anbindung von MIPI-Sensoren verschiedener Hersteller an FPGAs. Die IP basiert auf einer bestehenden D-PHY-Implementierung, die in der Regel von FPGA-Anbietern erhältlich ist. Die IP wird als voll funktionsfähiges Referenzdesign geliefert, das auf einer vereinbarten gemeinsamen Lieferplattform zusammen mit einem MIPI-FMC-Modul läuft, das mit dem MVDK von S2I und Standard-FPGA-Evaluierungskits kompatibel ist. Zusammen bieten sie eine einfache Möglichkeit, eine Kamera zu entwerfen.

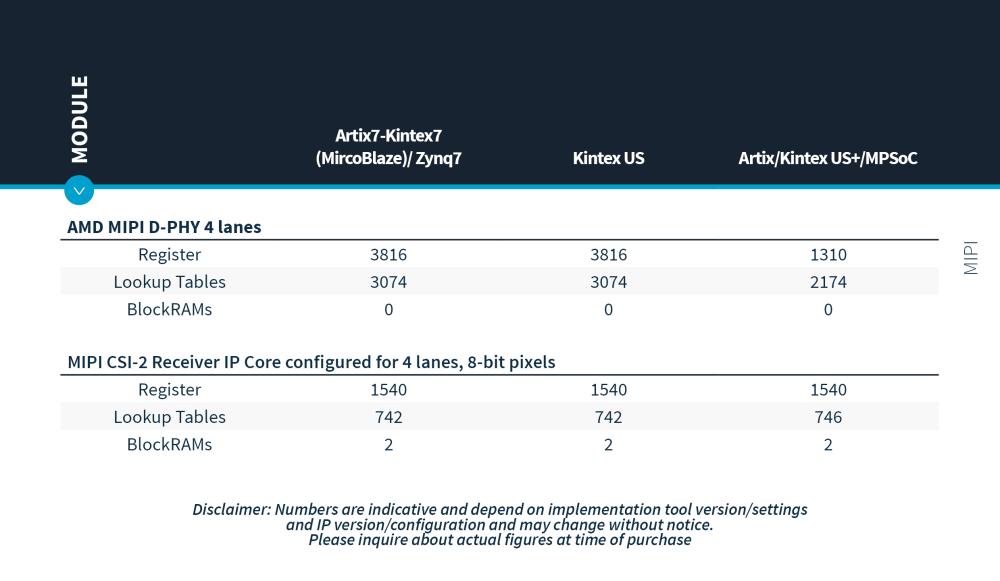

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

MVDK mit MIPI CSI-2-Schnittstellenkarte

Hauptmerkmale

- FPGA-Technologieunabhängig

- PPI-Schnittstelle zum Anschluss an verschiedene D-PHY-Implementierungen

- Konfigurierbar für 1, 2 oder 4 Datenkanäle

- Beliebige Lane-Rate (begrenzt durch den verwendeten FPGA)

- RAW8, RAW10, RAW12, RAW14, RAW16 Standard-MIPI-Datentypen

- Eingebettete Datendekodierung

- Direkte Ausgabe des neu angeordneten Byte-Streams ohne Pixel-Entpackung

- AXI4-Lite-Slave-Steuerschnittstelle

Lieferung

Der IP Core wird mit einem vollständigen Referenzdesign für den MVDK von S2I mit einem Zynq7- oder Ultrascale+-FPGA und einem IMX-MIPI-FMC-Modul geliefert. Da die physikalische Schnittstelle durch den AMD-D-PHY-Core abstrahiert wird, lässt sich das Design leicht auf andere FPGA-Plattformen portieren, wie beispielsweise die AMD-FPGAs der Serie 7.

Verfügbare Module

Der MIPI CSI-2 Receiver IP Core wird als verschlüsseltes VHDL geliefert. Er ist optional als VHDL-Quellcode erhältlich. Er ist kompatibel mit AMD Artix7, Kintex7, Zynq7 und Ultrascale+ FPGAs. Die MIPI CSI-2 Receiver IP Software-Bibliothek wird als Objektdatei geliefert. Sie ist optional als C-Quellcode erhältlich.