GigE Vision Host-IP Core

GigE Vision Host-IP Core für FPGA

- Kompakt

- Anpassbar

- Kompatibel mit AMD 7 Series (und neuer) und Altera Cyclone 10-Geräten (und neuer)

- Unterstützt Geschwindigkeiten von 1 Gbit/s bis zu mehr als 10 Gbit/s

- Wird als eigenständiges, voll funktionsfähiges Referenzdesign geliefert

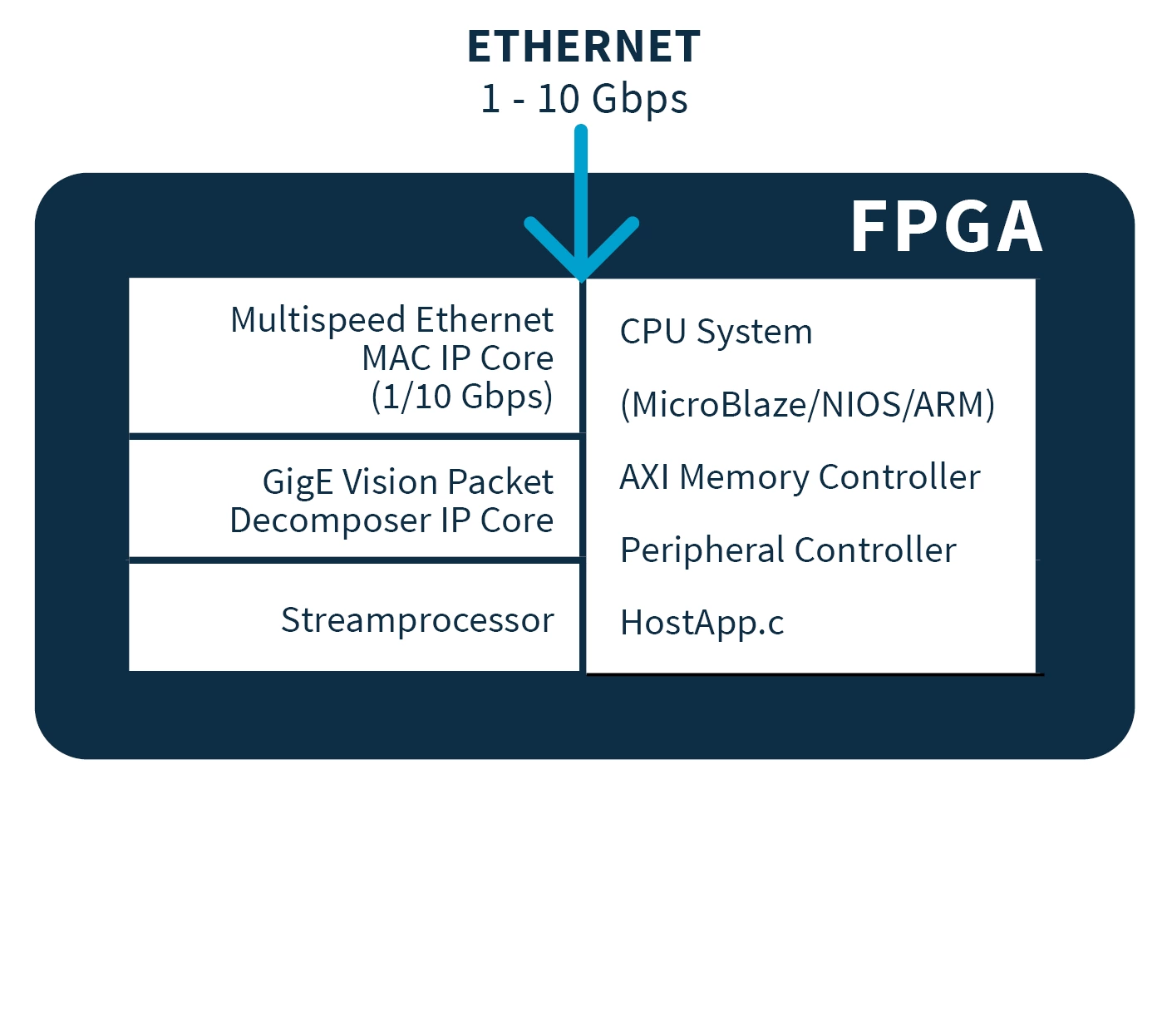

Architektur

GigE Vision ist ein Standard-Kommunikationsprotokoll für Bildverarbeitungsanwendungen, das auf der bekannten Ethernet-Technologie basiert. Es ermöglicht eine einfache Anbindung von GigE Vision-Geräten an PCs, die mit der TCP/IP-Protokollfamilie arbeiten. Sensor to Image bietet eine Reihe von IP Cores und ein Entwicklungsframework zum Aufbau von FPGA-basierten Empfängerprodukten unter Verwendung der GigE Vision-Schnittstelle. Aufgrund der Geschwindigkeit von GigE Vision, insbesondere bei Geschwindigkeiten über 1 Gbit/s, erfordern Empfänger eine schnelle FPGA-basierte Implementierung des eingebetteten GigE-Kerns. Der GigE Vision-Kernsatz ist mit Geräten von AMD und Altera kompatibel.

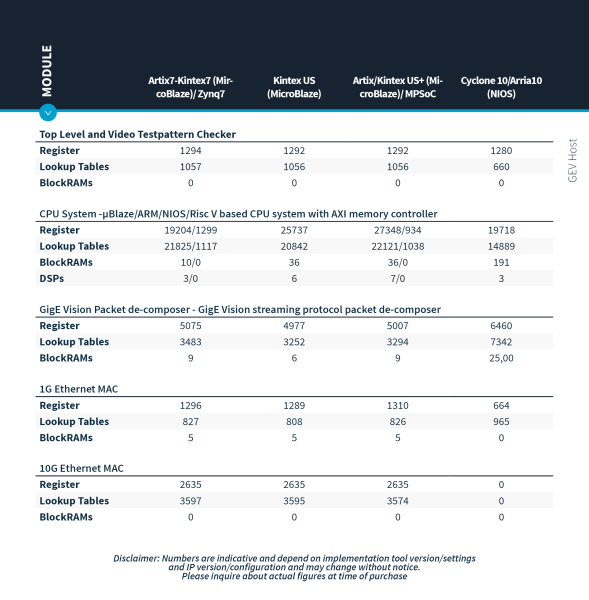

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

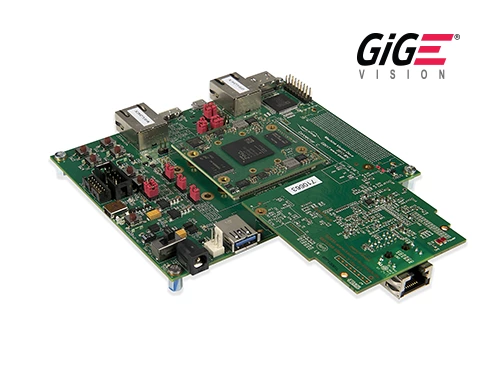

Breite Unterstützung für FPGA-Entwicklungskits

Die FPGA-IP Cores von Sensor to Image werden als voll funktionsfähige Referenzdesigns auf einem FPGA-Entwicklungskit geliefert. Wir unterstützen eine Vielzahl von handelsüblichen Kits von AMD, Altera und Microchip.

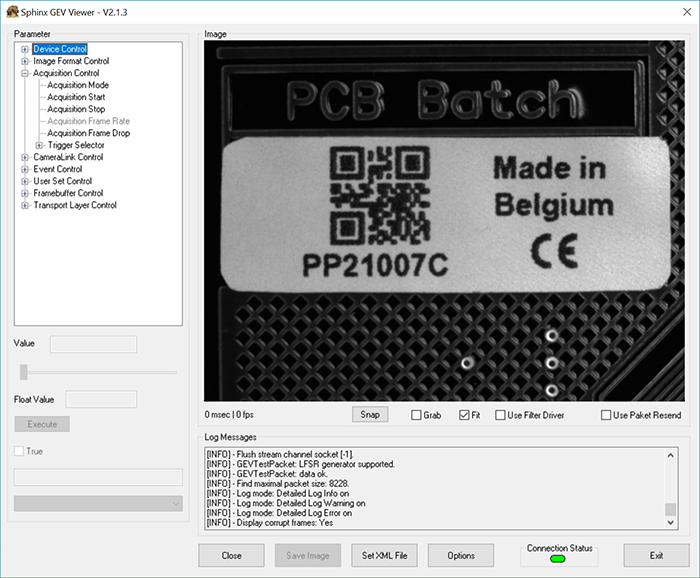

Sphinx SDK enthalten

Ein funktionsreiches Software-Toolkit, das die Bausteine für die schnelle und einfache Entwicklung leistungsstarker Videoanwendungen mit minimalem CPU-Ressourcenverbrauch bereitstellt. Dazu gehören auch ein Software Treiber und eine Erfassungsbibliothek für Windows oder Linux sowie Beispielanwendungen, darunter ein GigE Vision/GenICam-kompatibler Viewer.

Multistream-Unterstützung

Die GigE Vision Host IP kann mehrere Datenströme über eine Verbindung empfangen. Dies ist nützlich, um Bilddaten von mehreren Kameras zu erfassen. Beachten Sie, dass es für diesen Anwendungsfall dringend empfohlen wird, Linux auf der eingebetteten CPU auszuführen.

Mitgeliefertes Referenzdesign

Voll funktionsfähiges Referenzdesign: Die FPGA-Lösungen von S2I werden als eigenständiges, voll funktionsfähiges Referenzdesign geliefert, das auf einer vereinbarten gemeinsamen Plattform zusammen mit FPGA-IP Cores läuft. Dies minimiert die Entwicklungszeit und ermöglicht eine erstklassige Leistung bei geringem Platzbedarf, während gleichzeitig genügend Flexibilität für die Anpassung des Designs bleibt. Die Sensor-to-Image-Kerne sind kompakt und lassen genügend Platz im FPGA für Ihre Anwendung.

Top-Level-Design

Die erste Komponente des IP Cores ist das Top-Level-Design. Es handelt sich dabei um eine Schnittstelle zwischen externer Hardware (Imager, Sensoren, GigE PHY) und der internen Datenverarbeitung des FPGA. Wir liefern dieses Modul als VHDL-Quellcode, der an kundenspezifische Hardware angepasst werden kann.

C-Quellcode für Softwarebibliothek

Die eingebettete GigE Vision-Bibliothek des GigE Vision IP Core kann optional als Quellcode geliefert werden. Dies ist nützlich, um die Funktionalität für selten genutzte optionale GigE Vision-Funktionen zu erweitern oder die Hardwareanforderungen besser anzupassen. Ein zusätzlicher Software Treiber ermöglicht die Verwendung von Linux auf dem Gerät.

GigE-Paket-Dekomponierer

Der GigE Packet De-Composer extrahiert die Video- und Steuerdaten aus dem Paketstrom. Der GigE Packet De-Composer sendet alle GigE Vision-Steuerdaten an das CPU-System und gibt die GigE Vision-Streamingdaten als AXI-Stream aus.

Sphinx GigE Vision Server

Die Lieferung umfasst den Sphinx GigE Vision Server, einen Software-Kamerasimulator. Der Sphinx GigE Vision Server hilft dabei, sich schnell mit dem Design-Ablauf vertraut zu machen, und zeigt, wie die Kommunikation mit Kameras von Drittanbietern funktioniert.

Stream-Verarbeitungsmodul

Als Beispiel für die Videoverarbeitung enthält das Referenzdesign eine einfache Anzeigeeinheit oder ein Musterprüfmodul, das die Verwendung des Videostream-Ausgangs der GigE Packet De-Composer-Einheit demonstriert.

FPGA-integrierte CPU

Ein FPGA-integriertes CPU-Design (MicroBlaze, NIOS, ARM, Risc V) wird für verschiedene nicht zeitkritische Netzwerk- und Konfigurationsaufgaben verwendet. Es implementiert auch das GigE Vision Control Protocol (GVCP). Diese Software ist in C geschrieben und kann vom Kunden erweitert werden.

FMC-Schnittstellenerweiterungen

Um die Funktionalität der verschiedenen Referenzplatinen zu erweitern, bieten wir FMC-Karten für 1G-Ethernet und 10G-Ethernet mit NBaseT-Unterstützung an.