GigE Vision-Geräte-IP Core

GigE Vision-Geräte-IP Core für FPGA

- Kompakt

- Anpassbar

- Kompatibel mit AMD 7 Series (und neuer)

- Kompatibel mit Altera Cyclone V-Geräten (und neuer)

- Vorläufige Kompatibilität mit Microchip PolarFire

- Geschwindigkeitsunterstützung von 1 Gbit/s bis über 10 Gbit/s

- Lieferung als eigenständiges, voll funktionsfähiges Referenzdesign

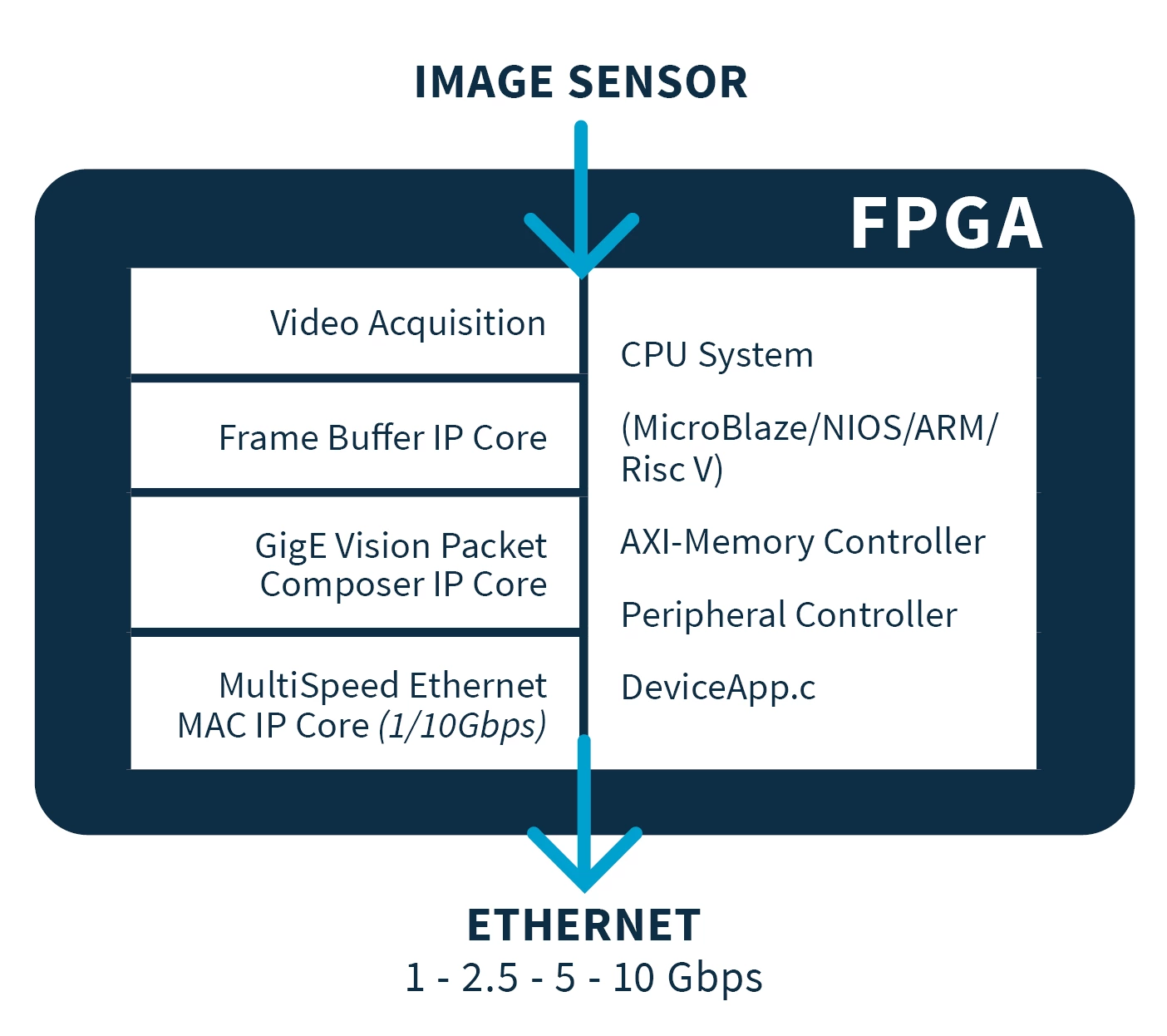

Architektur

GigE Vision ist ein Standard-Kommunikationsprotokoll für Bildverarbeitungsanwendungen, das auf der bekannten Ethernet-Technologie basiert. Es ermöglicht eine einfache Anbindung von GigE Vision-Geräten an PCs, die mit der TCP/IP-Protokollfamilie arbeiten. Sensor to Image bietet eine Reihe von IP Cores und ein Entwicklungsframework für die Erstellung von FPGA-basierten Senderprodukten mit GigE Vision-Schnittstelle. Aufgrund der Geschwindigkeit von GigE Vision, insbesondere bei Geschwindigkeiten über 1 Gbit/s, benötigen Sender eine schnelle FPGA-basierte Implementierung des eingebetteten GigE-Cores. Der GigE Vision-Core-Satz ist kompatibel mit Geräten der AMD 7-Serie (und neuer), Altera Cyclone V-Geräten (und neuer) und Microchip PolarFire.

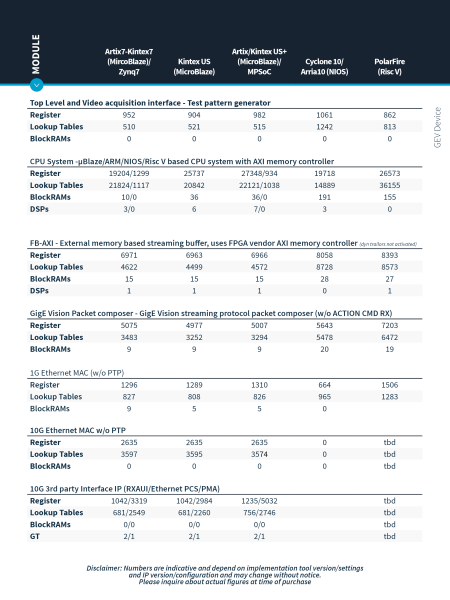

Ressourcenverbrauch

Ressourcenverbrauch herunterladenVorteile

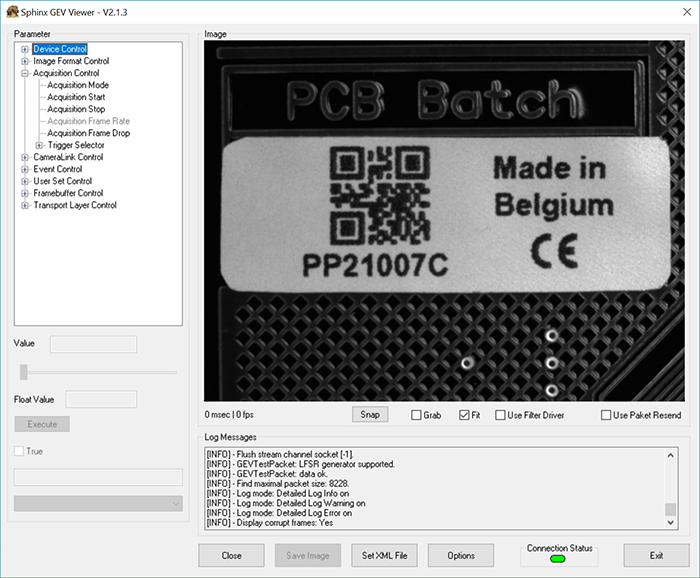

Sphinx SDK enthalten

Ein funktionsreiches Software-Toolkit, das die Bausteine für die schnelle und einfache Entwicklung leistungsstarker Videoanwendungen mit minimalem CPU-Ressourcenverbrauch bereitstellt. Dazu gehören auch ein Software Treiber und eine Erfassungsbibliothek für Windows oder Linux sowie Beispielanwendungen, darunter ein GigE Vision/GenICam-kompatibler Viewer.

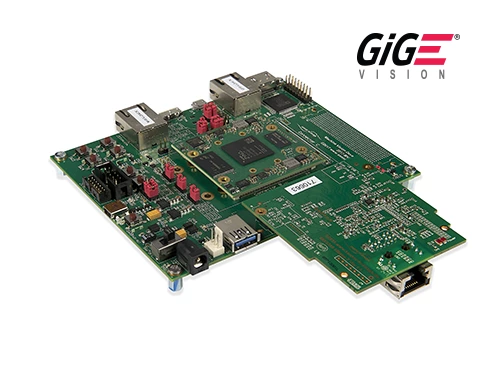

Breite Unterstützung für FPGA-Entwicklungskits

Die FPGA-IP Cores von Sensor to Image werden als voll funktionsfähige Referenzdesigns auf einem FPGA-Entwicklungskit geliefert. Wir unterstützen eine Vielzahl von handelsüblichen Kits von AMD, Altera und Microchip.

GenDC-Unterstützung

Der GigE Vision IP Core bietet die Option, den leistungsstarken und sehr flexiblen GenDC-Nutzlasttyp zu unterstützen. Dies ist nützlich, um komplexe Datenstrukturen zu übertragen, die häufig in 3D-Anwendungen verwendet werden.

Mitgeliefertes Referenzdesign

Voll funktionsfähiges Referenzdesign: Die FPGA-Lösungen von S2I werden als eigenständiges, voll funktionsfähiges Referenzdesign geliefert, das auf einer vereinbarten gemeinsamen Plattform zusammen mit FPGA-IP Cores läuft. Dies minimiert die Entwicklungszeit und ermöglicht eine erstklassige Leistung bei geringem Platzbedarf, während gleichzeitig genügend Flexibilität für die Anpassung des Designs bleibt. Die Sensor-to-Image-Kerne sind kompakt und lassen genügend Platz im FPGA für Ihre Anwendung.

ACTION-Befehlsdecoder mit geringer Latenz

Der GigE Vision IP Core verfügt über die Option eines hardwareimplementierten Decoders für den GigE Vision ACTION-Befehl. Dies ermöglicht Ad-hoc-Trigger mit geringer Latenz und geringem Jitter.

Top-Level-Design

Die erste Komponente des IP Core ist das Top-Level-Design. Es handelt sich dabei um eine Schnittstelle zwischen externer Hardware (Imager, Sensoren, GigE PHY) und der internen Datenverarbeitung des FPGA. Wir liefern dieses Modul als VHDL-Quellcode, der an kundenspezifische Hardware angepasst werden kann.

FPGA-integrierte CPU

Ein FPGA-integriertes CPU-Design (MicroBlaze, NIOS, ARM, Risc V) wird für verschiedene nicht zeitkritische Netzwerk- und Konfigurationsaufgaben verwendet. Es implementiert auch das GigE Vision Control Protocol (GVCP). Diese Software ist in C geschrieben und kann vom Kunden erweitert werden.

Multistream-Unterstützung

Der GigE Vision IP Core bietet die Möglichkeit, mehrere Datenströme über eine einzige Verbindung zu übertragen. Dies ist nützlich, um unabhängige Daten aus verschiedenen Datenquellen über ein einziges Kabel zu übertragen.

Videoerfassungsmodul

Das Videoerfassungsmodul des Referenzdesigns simuliert eine Kamera mit einem Testbildgenerator. Dieses Modul wird als VHDL-Quellcode geliefert, der im endgültigen Kameradesign durch eine Sensorschnittstelle und eine Pixelverarbeitungslogik ersetzt werden muss.

Benutzerdefinierte Konfiguration

Einige Teile des Designs werden nur als Binärdateien geliefert (z. B. die GigE Vision-Steuerungsprotokollbibliothek), während andere Teile als Quellcode geliefert werden. Das Design-Framework enthält alle erforderlichen Designdateien und Kerne sowie Vivado- oder Quartus-Projektdateien. Es ist als GigE Vision-Kamerasystem mit einem konfigurierbaren Testmustergenerator konfiguriert. Dieses System wird als Referenzdesign für ein handelsübliches Evaluierungsboard geliefert. Das Referenzdesign verwendet die Entwicklungswerkzeuge von AMD oder Altera (nicht im Lieferumfang enthalten).

Bildspeicher

Ein Framebuffer ist mit dem herstellerspezifischen Speichercontroller des FPGA verbunden. Der Framebuffer ermöglicht Frame-Pufferung und Bildpaketierung. Dies ist für die Implementierung der Paket-Wiederholungsfunktion erforderlich. Dieses Modul verwendet in der Regel externen Speicher, könnte jedoch mit eingeschränkter Funktionalität auch mit dem internen Speicher des FPGA realisiert werden.

C-Quellcode für Softwarebibliothek

Die eingebettete GigE Vision-Bibliothek des GigE Vision IP Core kann optional als Quellcode geliefert werden. Dies ist nützlich, um die Funktionalität für selten genutzte optionale GigE Vision-Funktionen zu erweitern oder die Hardwareanforderungen besser anzupassen. Ein zusätzlicher Software Treiber ermöglicht die Verwendung von Linux auf dem Gerät.

GigE-Paket-Komponist

Der GigE Packet Composer generiert die endgültigen Stream-Pakete mit allen von der GigE Vision-Transportschicht benötigten Headern. Der GigE Packet Composer sendet alle Daten an den Ethernet-MAC und implementiert das Hochgeschwindigkeits-GigE Vision Streaming Protocol (GVSP).

IEEE1588-Unterstützung

Der GigE Vision IP Core verfügt über die Option, seine Zeitbasis mit einer externen IEEE1588-Zeitquelle zu synchronisieren. Dies ist für eine präzise zeitgesteuerte Auslösung ohne zusätzliche Verkabelung erforderlich. Wenn keine externe Zeitquelle verfügbar ist, kann das System selbst als Zeitquelle fungieren.

MAC

Eine MAC-Komponente ist mit der Low-Level-Transportschichttechnologie und der physikalischen Schicht verbunden. Sie ist für verschiedene Geschwindigkeiten von 1 Gbit/s bis zu 10 Gbit/s verfügbar und kann gemäß dem IEEE1588-Protokoll das Packet Stamping unterstützen.

FMC-Schnittstellenerweiterungen

Um die Funktionalität der verschiedenen Referenzplatinen zu erweitern, bieten wir FMC-Karten für 1G-Ethernet und 10G-Ethernet mit NBaseT-Unterstützung an.