- MIPI CSI-2接收器与解码模块

- 可配置的MIPI通道数量

- 采用AMD D-PHY IP

- 以可运行的参考设计形式交付,实现快速开发

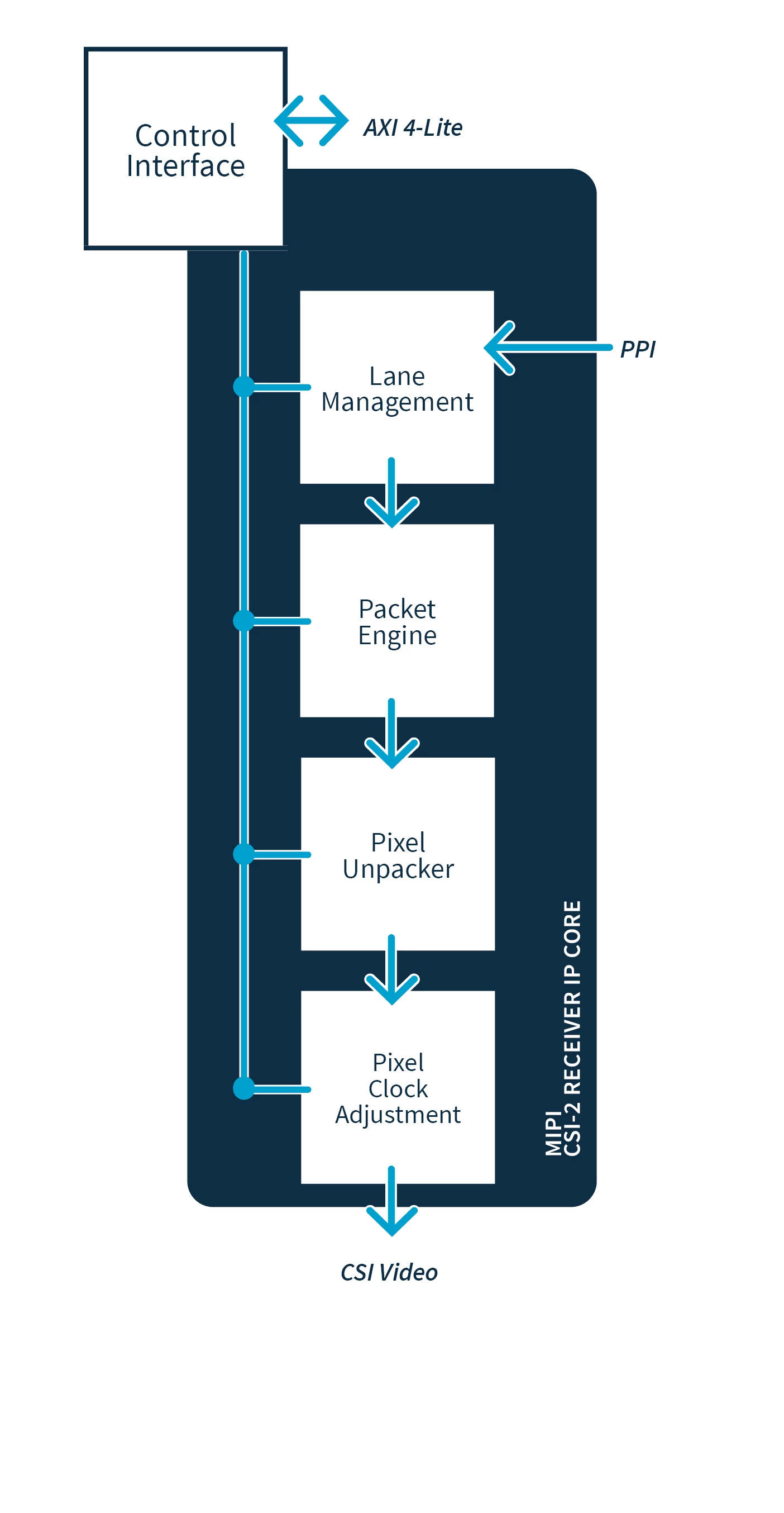

建筑

采用MIPI接口的图像传感器不仅应用于手机领域,还广泛用于工业和汽车领域。这些应用场景通常需要通过FPGA实现控制与后续处理。本IP可将不同厂商的MIPI传感器与FPGA进行接口连接,其设计基于现有D-PHY实现方案(通常由FPGA厂商提供)。 该IP以完整功能的参考设计形式交付,可在约定通用交付平台上运行,并配备兼容S2I MVDK及标准FPGA评估套件的MIPI FMC模块。二者结合为相机设计提供了便捷方案。

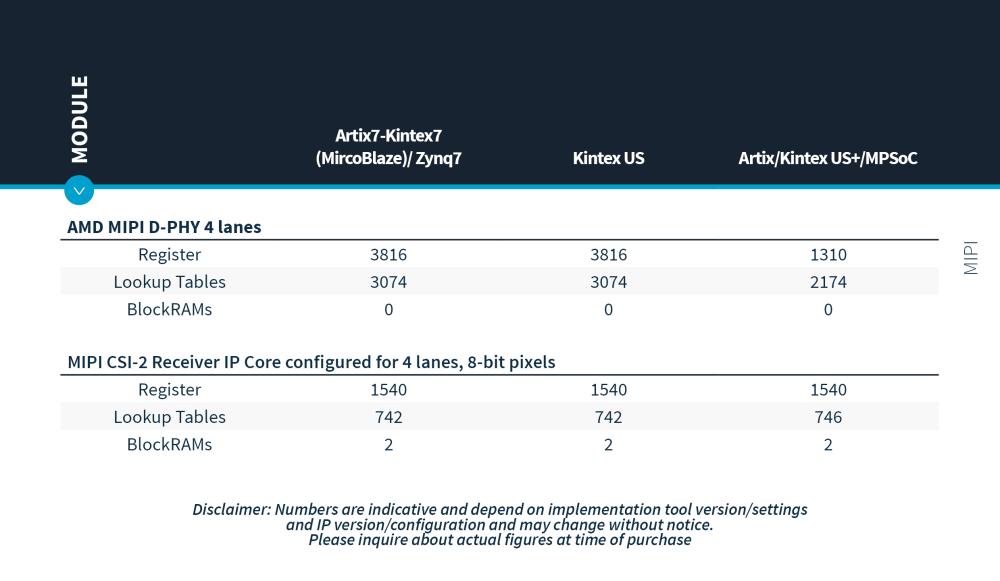

资源使用情况

下载资源使用情况福利

MVDK 带 MIPI CSI-2 接口板

主要特点

- FPGA技术无关

- PPI接口用于连接不同D-PHY实现方案

- 可配置为1、2或4条数据通道

- 支持任意通道速率(受所用FPGA限制)

- RAW8、RAW10、RAW12、RAW14、RAW16标准MIPI数据类型

- 嵌入式数据解码

- 无需像素解包即可直接输出重新排序的字节流

- AXI4-Lite从机控制接口

配送

该IP核随附完整的参考设计,适用于搭载Zynq7或Ultrascale+ FPGA及IMX MIPI FMC模块的S2I MVDK开发板。由于物理接口由AMD D-PHY核心进行抽象处理,该设计可轻松移植至其他FPGA平台,例如AMD 7系列FPGA。

可用模块

MIPI CSI-2接收器IP核以加密VHDL形式交付,也可选配VHDL源代码版本。该IP核兼容AMD Artix7、Kintex7、Zynq7及Ultrascale+系列FPGA。MIPI CSI-2接收器IP软件库以对象文件形式交付,也可选配C源代码版本。